第4世代 Xeon スケーラブル・プロセッサー ”Sapphire Rapids” 搭載

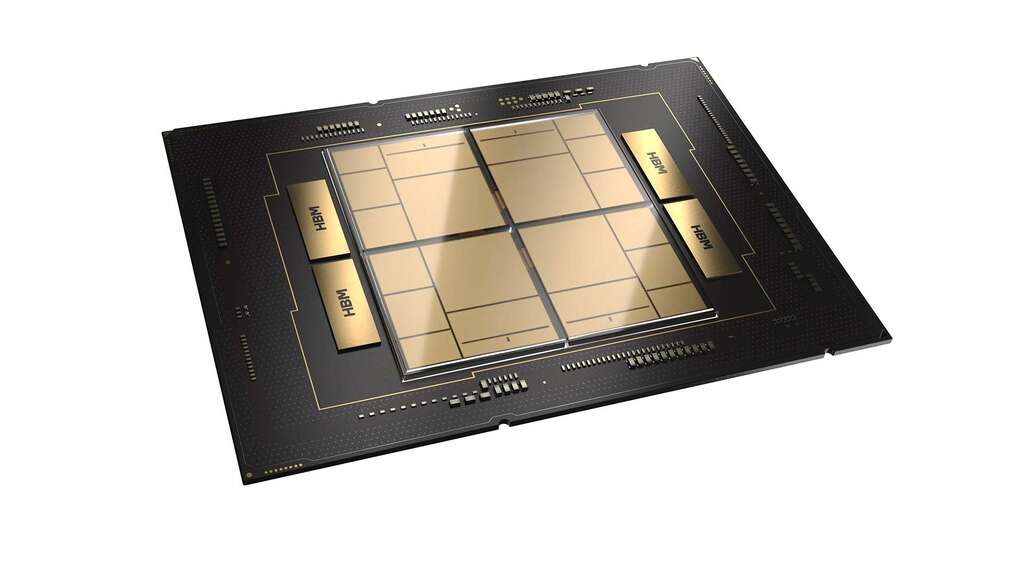

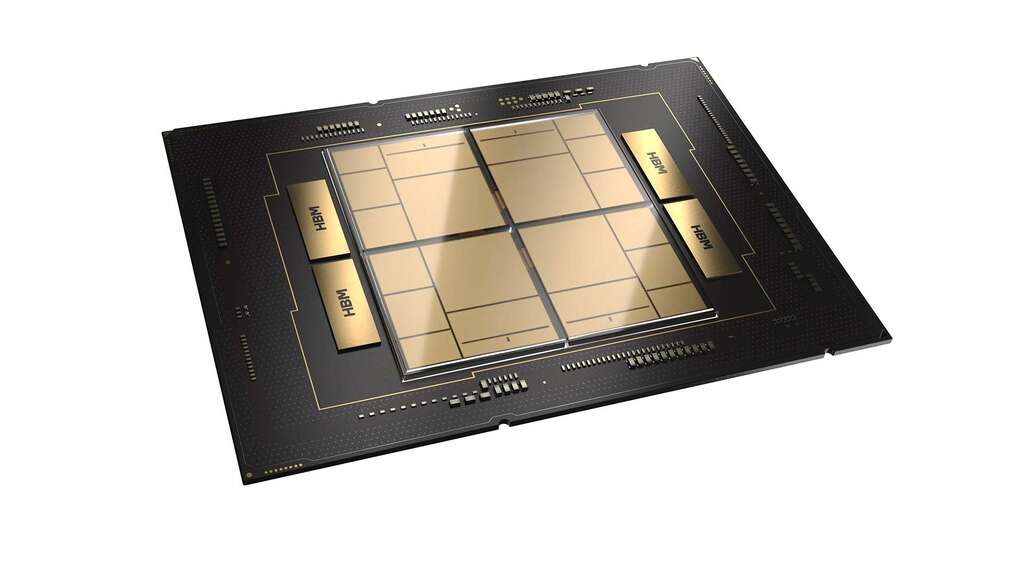

第4世代Xeonスケーラブルプロセッサは、4つのCPUダイを1つのパッケージに統合するチップレット技術を採用しており、Intelが独自開発したEMIBを利用して4つダイが1つの巨大CPUとして動作します。この技術により従来製品では最大40コアだったCPUコア数は、最大60コアへと強化されました。

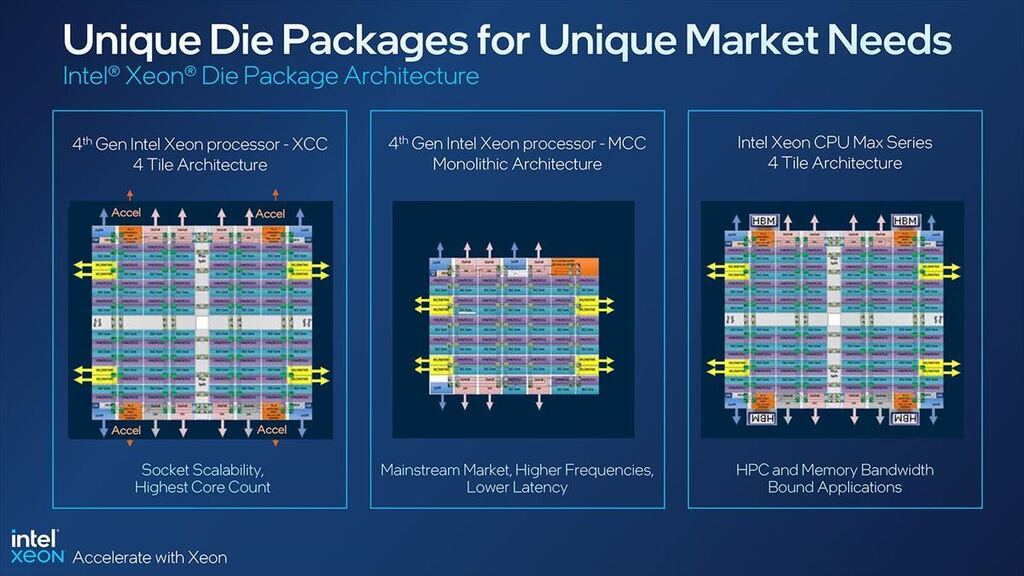

3種類のダイ・パッケージ

第4世代Xeonスケーラブルプロセッサには、3種類のダイ・パッケージが存在します。4つのチップレットで構成されたXCC、1つのチップレットで構成されたMCC、及び、広帯域なHBM2eメモリを備えるインテル Xeon CPUマックス・シリーズです。インテル Xeon CPUマックス・シリーズでは、64GBのHBM2eをパッケージ上に実装し、HPCとAIのワークロードでデータ・スループットを大幅に向上させます。

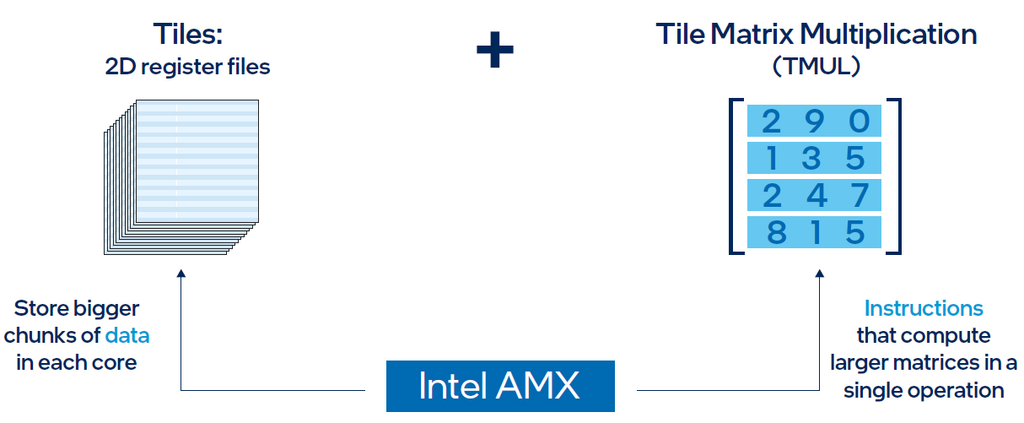

新命令セット Intel AMX 搭載

Intel AMXとは、複数の行列をまとめて計算するために設計された拡張命令です。Intel AMXのアーキテクチャは、2つのコンポーネントで構成されています。

1つ目のコンポーネントはタイルです。タイルは8つの2次元レジスタで構成され、それぞれが1キロバイトの大きさです。大きなデータチャンクを格納するのデータを格納します。

2つ目のコンポーネントは「Tile Matrix Multiplication(TMUL)」で、TMULはタイルに付属するアクセラレータエンジンであり、行列の乗算計算を行います。TMULはタイルに取り付けられたアクセラレータエンジンで、AIのための行列乗算の計算を行います。

新旧Xeonの比較表

| 第3世代Xeonスケーラブルプロセッサ | 第4世代Xeonスケーラブルプロセッサ | |

| Socket Count | 1 and 2 | 1S, 2S, 4S, & glueless 8S (>8S via xNC support) |

| Die Size | 10nm | 10nm enhanced SuperFin (Intel7) |

| 最大コア数 | 40コア (HT有効時 80コア) per socket | 60コア (HT有効時 120コア) per socket |

| キャッシュ | First Level Cache: 32 KB Instruction Cache 48 KB Data Cache Mid-Level Cache: 1.25 MB private per core Last Level Cache: 1.5 MB per core | First Level Cache: 32 KB Instruction Cache 48 KB Data Cache Mid-Level Cache: 2 MB private per core Last Level Cache: 1.875 MB per core |

| TDP | 最大270W | 最大350W |

| Physical/Virtual address bits | 52 / 57 | 52 / 57 |

| Memory controllers / Sub-Numa clusters | 4 / 2 | 4 / 4 |

| Memory | Up to 8 channels DDR4 per CPU Up to 16 DIMMs per socket Up to 3200 MT/s 2DPC | Up to 8 channels DDR5 per CPU Up to 4400 MT/s 2DPC Up to 4800 MT/s 1DPC |

| Number of Intel® Ultra Path Interconnect (Intel® UPI) Interconnects | Up to 3 links per CPU (x20 wide) | Up to 4 links per CPU (x24 wide) |

| Intel® UPI Interconnect Speed | Up to 11.2 GT/s | Up to 16 GT/s |

| PCIe | Up to 64 lanes per CPU (bifurcation support: x16, x8, x4) PCIe Gen 4 support | 80 PCIe lanes with Flex Bus/CXL** – per CPU PCIe Gen 5.0 support (NTB @ PCIe 4.0) 48 lanes North/ 32 lanes South of socket PCIe bifurcation support: x16, x8, x4, x2(Gen4) Intel® Scalable I/O Virtualization (Intel® Scalable IOV) |